Nächste Seite: D-FF Aufwärts: 2024-11-28 Vorherige Seite: in VHDL

-- (C) David Vajda

-- D-Latch

-- 2024-11-28

library ieee;

use ieee.std_logic_1164.all;

entity rslatch20241128 is

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end;

architecture behaviour of rslatch20241128 is

begin

q <= (r nor p);

p <= (s nor q);

end;

library ieee;

use ieee.std_logic_1164.all;

entity clktriggeredrslatch20241128 is

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of clktriggeredrslatch20241128 is

component rslatch20241128

port (

r: in std_logic;

s: in std_logic;

q: inout std_logic;

p: inout std_logic

);

end component;

signal e, d: std_logic;

begin

rs: rslatch20241128 PORT MAP (r=>e, s=>d, q=>q);

d <= c and s;

e <= c and r;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch20241128 is

port (

d: in std_logic;

c: in std_logic;

q: inout std_logic

);

end;

architecture behaviour of dlatch20241128 is

component clktriggeredrslatch20241128

port (

r: in std_logic;

s: in std_logic;

c: in std_logic;

q: inout std_logic

);

end component;

signal e, f: std_logic;

begin

clkrs: clktriggeredrslatch20241128 PORT MAP (r=>f, s=>e, c=>c, q=>q);

e <= d;

f <= not d;

end;

library ieee;

use ieee.std_logic_1164.all;

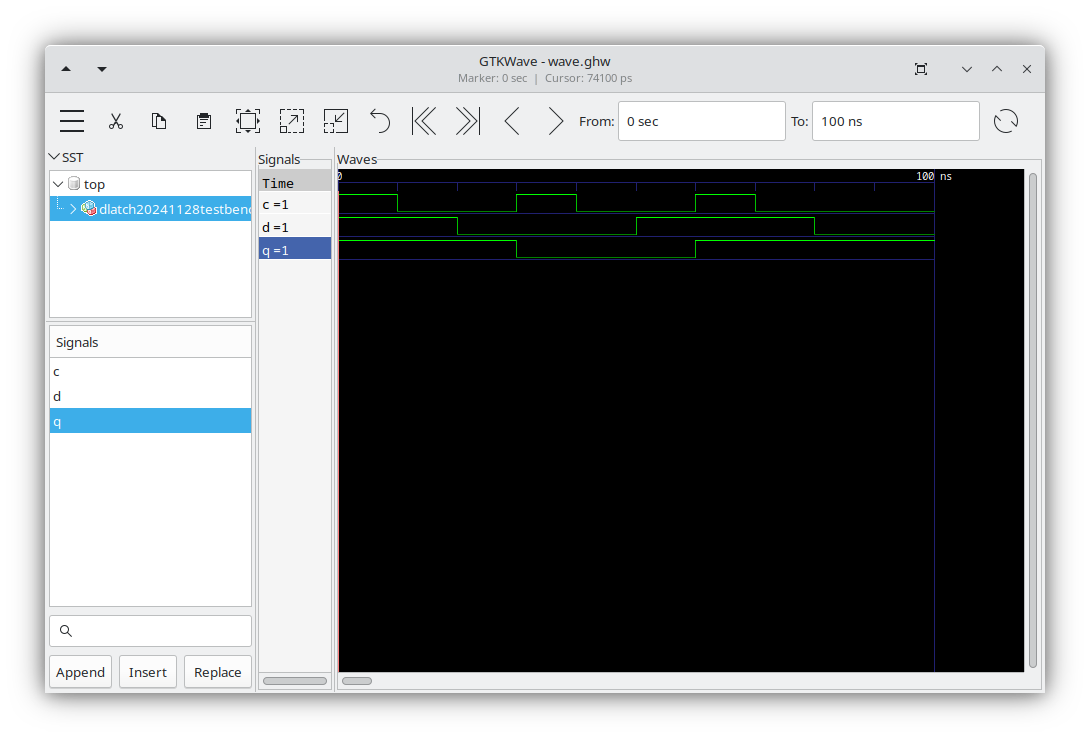

entity dlatch20241128testbench is

port (

q: inout std_logic

);

end;

architecture behaviour of dlatch20241128testbench is

component dlatch20241128

port (

c: in std_logic;

d: in std_logic;

q: inout std_logic

);

end component;

signal d, c: std_logic;

begin

dl: dlatch20241128 PORT MAP (d=>d, c=>c, q=>q);

-- diese sind aus dem letzten eingefuegt, damit ich sie nicht noch mal schreiben muss

d <= '1' after 0 ns, '1' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

c <= '1' after 0 ns, '0' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '0' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns;

end;

|